# **Designing of Double-Gate MOSFET for Low Power RFID**

#### Nidhi Malhotra

Department of Electronics and Communication Engineering Faculty of Engineering, Teerthanker Mahaveer University, Moradabad, Uttar Pradesh, India

ABSTRACT: Recently, dual gate MOSFETs (DGMOSFETs) have been demonstrated to be more ideal for ultra-low force circuit structure due to the improved subthreshold incline and the diminished spillage current contrasted with mass CMOS. In any case, DGMOSFETs for subthreshold circuit configuration have not been highly investigated in contrast with those for solid reversal based structure. In this paper, different setups of DGMOSFETs, for example, tied/free doors and symmetric/topsy-turvy entryway oxide thickness are investigated for ultra-low force and high proficient radio recurrence recognizable proof (RFID) structure. Examination of mass CMOS with DGMOSFETs has been directed in ultra-low force subthreshold computerized rationale structure and rectifier configuration, underscoring the extent of the Nano-scale DGMOSFET innovation for future ultra-low force devices. The DGMOSFET-based subthreshold rationale improves vitality effectiveness by over 40% contrasted with the mass CMOS-based rationale at 32 nm. Among the different DGMOSFET arrangements for RFID rectifiers, symmetric tied-door DGMOSFET has the best force change proficiency and the least force utilization.

KEYWORDS: Autonomous Door DGMOSFET, Gadget/Circuit Co-Structure, High Effective Rectifier for RFID, Subthreshold Rationale, Ultra-Low Force, Uneven DGMOSFET.

### INTRODUCTION

One of the essential inspirations driving changing innovation from bipolar transistors to MOSFETs is that the low force utilization of CMOS circuits alongside little size makes joining conceivable. MOSFETs joined with innovation scaling made the IC business fruitful in view of the diminished power, diminished region, sped up, and ease per chip. As the quantity of transistors that are coordinated per chip expands, issues like spillage current, power scattering, heat expulsion, cooling methods, and unwavering quality have been raised. These have expanded the interest for power-compelled or vitality obliged structure for current VLSI devices rather than past clock speed driven devices [1].

There is an expanding class of utilizations like compact hardware, smaller scale sensors, radio recurrence distinguishing proof (RFID), and implantable biomedical gadgets, which request ultra-low force utilization and delayed battery lifetime. These worries on power decrease spurred the fashioners to think of intensity decrease strategies, for example, supply voltage scaling, exchanging action decrease, structural systems of pipelining and parallelism, PC helped plan (CAD) systems for gadget estimating and interconnect, rationale improvement, and so on. Among these systems, the most effectively demonstrated strategy is the stockpile voltage scaling, which fundamentally lessens both dynamic and static parts of intensity [2].

An outrageous case in supply voltage scaling is the subthreshold activity where the stock voltage is not exactly the edge voltage of gadgets. It has been demonstrated that base vitality per activity is accomplished by working circuits in the subthreshold area. Sub-edge circuits work with an inventory voltage that is not exactly the edge of the transistors—far underneath customary levels and therefore the transistors work basically on subthreshold current. While customary computerized rationale has depended on running transistors either in the ON state (solid reversal) or OFF state (subthreshold), subedge circuits are either in an OFF state or a frail OFF state (still in sub-limit system yet with feeble reversal). Despite the fact that subthreshold activity is restricted in execution, it stays adequate for low to medium execution and vitality productive compelled applications, for example, RFID, remote miniaturized scale sensors, biomedical inserts, and so forth.

RFID labels work in a few groups—high-recurrence (HF), ultra-high-recurrence (UHF) and microwave groups. Transponders that work at 125 kHz and 13.56 MHz have been sent for various years. Their hindrance is constrained range. Uninvolved transponders that work in the UHF band have scopes of 7.5–9 m, and transponders that work in the microwave band have goes under 2 m. A researcher revealed a low force RFID chip for UHF with low force utilization. This is accomplished by the mix of heartbeat width balance on the forward connection (base-station to tag) with low RF-off occasions (no overabundance voltage hang on the on-chip power capacitor) and, stage move keying (PSK) on the arrival connect (tag to base-station). An elevated level depiction of aloof RFID chip that executes the EPC Class 0 convention.

A researcher gave structure models to the front-finish of latent RFID labels. While the range for detached RFID labels at UHF and microwave is sufficient for certain applications, more prominent range is emphatically required. Dynamic transponders give more prominent range, however they require a battery and as needs be have a restricted lifetime. Besides the battery ought to have a little structure factor with the goal that it very well may be consistently utilized in the gathering procedure for enormous volume creation. The long lifetime (for the most part in abundance of 10 years) and the little battery limit require ultra-low force utilization on the dynamic transponder to work all through the full existence of the tag [3]. Different research about CMOS front-finishes and CMOS innovation for RFID has been distributed. Be that as it may, not very many have considered dual gate MOSFETs (DGMOSFETs) for the ultra-low force RFID label structure.

While advanced device configuration has consistently pushed for the expanded speed of least size gadgets, simple fashioners have frequently utilized longer channels to maintain a strategic distance from short channel impacts (SCEs) and accomplish higher voltage gain. As simple gadgets are scaled into the Nano-meter system, CMOS advancements will require inventive gadget structures and plan systems to accomplish fantastic simple measurements. The value of non-classical underlap channel engineering to improve both increase and transfer speed of an OTA, reducing gain-transmission capacity exchange off related with simple structure. Researchers investigate utilizations of freely determined DGMOSFETs (IDGMOSFETs) for low-force and low-voltage simple incorporated circuit plan. In back-door setup, the second entryway of DGMOSFET can be utilized to tune the limit voltage of the gadget. A straightforward and cascade current mirror dependent on mass driven transistor is updated with DGMOSFETs and appeared to have littler information voltage drop and lower power utilization.

Capacity of dynamic limit tuning is misused to plan a versatile two-phase operational intensifier (operation amp) which can work at voltages as low as 0.5 V without giving up execution parameters. They investigated new capacities welcomed on by IDGMOSFETs for simple baseband structure. Since the two entryways are separated, the relating directs are coupled bringing about a dynamic edge voltage tuning. This activity mode is misused to make new simple capacities and low-voltage circuits. A present mirror is upgraded utilizing IDGMOSFETs and it is indicated that this structure plays out a productive differential capacity identifying with the possibilities applied to the back doors. Being adjusted to low-voltage activity and self-remunerated from input basic mode varieties, the differential current mirror is utilized for the dynamic stacking of a low-voltage completely adjusted OTA. They research the impact of both channel and entryway building on the simple and RF exhibitions of DGMOSFETs for device on-chip applications. The door designing procedure utilized here is the double metal entryway innovation, and the channel building strategy is the ordinary corona doping process.

Much work has likewise been done to explore the extent of different multi-door MOSFET structures. A few usage of multi-entryway structures incorporate "Depleted Lean-channel Transistor (DELTA), Gate-All Around gadget (GAA), Silicon-On-Nothing (SON) MOSFET", Multi-Fin XMOS (MFXMOS), triangular-wire SOI MOSFET, n-channel SOI MOSFET, four fold door or encompassing entryway gadgets having a width-to-stature proportion a lot nearer to solidarity, quantum-wire SOI MOSFET, trigate MOSFET, CYNTHIA gadget (roundabout segment gadget), column encompassing entryway MOSFET (square-segment gadget), planar encompassing door gadgets with square or roundabout cross segments. Albeit, hypothetically encompassing door MOSFETs may be more qualified for subthreshold rationale, yet at the current phase of research, according to ITRS long haul objectives, DGMOSFETs likely will supplant the current mass CMOS sooner rather than later also, mass CMOS scaling patterns are not in any case additionally remembered for the ITRS long haul

objectives. With this see, this work centres on DGMOSFETs for ideal ultra-low force subthreshold circuit plan [4].

In this paper, the researcher investigate the extent of tied/autonomous entryways and symmetric/topsyturvy doors of DGMOSFETs with circuit co-plan for strong ultra-low force RFIDs. The rest of this paper is composed as follows. DGMOSFETs for hearty and ultra-low force subthreshold circuit structure and examination with Nano-scale mass CMOS are depicted. Different DGMOSFET setups with circuit co-structure for ultra-low force subthreshold rationale configuration.

# TWOFOLD GATE MOSFETS (DGMOSFETS) FOR ULTRA-LOW POWER SUBTHRESHOLD CIRCUIT DESIGN

Presentation of Double-Gate MOSFETs (DGMOSFETs)

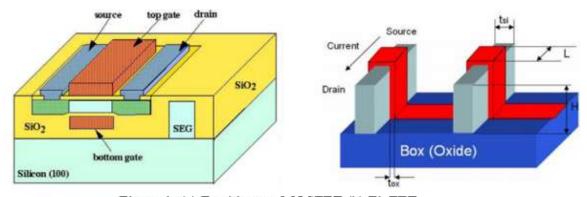

Better adaptability can be accomplished by presentation of a second door at the opposite side of the assemblage of every transistor bringing about a dual gate SOI structure. Because of the brilliant control of the short channel impacts, dual gate SOI gadgets have risen as the gadget of decision for circuit structure in sub-50 nm system. Low subthreshold spillage and higher ON-current in the dual gate gadgets make them reasonable for circuit configuration in sub-50 nm system. One of the promising structures in the twofold door innovation is Fin FET because of the basic manufacture process as described in Figure 1 [5].

Dual gate gadgets with confined doors (free entryways) are being created. The free door alternative can be helpful for low force and blended sign applications. Such improvements at the gadget level give chances to better approaches for circuit plan for low force and, superior. ITRS reports additionally show the unavoidable consideration of DGMOSFETs in up and coming VLSI applications. DGMOSFETs for ideal subthreshold tasks have likewise been considered as of late. DGMOSFETs are reasonable for the sub-limit activity because of their close to perfect subthreshold slant also, insignificant intersection capacitance. Due to the slim, completely drained silicon body sandwiched between two doors, these gadgets have a fantastic entryway authority over the channel. Besides, the unhoped meagre silicon body gives irrelevant source/channel p-n intersection capacitance, which to a great extent improves the circuit execution. By and large, DGMOSFETs have the accompanying points of interest over mass

### CMOS innovation:

- Nearly perfect subthreshold incline.

- Small inborn door capacitance. •

- Littler intersection capacitances.

- Better resistance to SCEs, albeit irrelevant for subthreshold activity.

- Reduced Random dopant changes (RDF) due to less doped or gently doped body and decreased transporter portability corruption.

- Higher ION/IOFF proportion.

- Design adaptability at circuit level by symmetric/unbalanced with tied and autonomous door alternatives.

Figure 1: (a) Double gate MOSFET (b) FinFET

Examination of Bulk CMOS and DGMOSFETs for Ultra-Low Power Subthreshold Circuit Design

#### a. Mass CMOS and DGMOSFET Device Model Parameters

The universal innovation guide for semiconductors (ITRS), which maps out close and long haul objectives for the semiconductor business, portrays three unique gadgets with various force defer tradeoffs: elite, low working force (LOP), and low backup power (LSTP). The Hack and LSTP gadgets are improved along these lines, despite the fact that the LSTP gadget has more severe spillage requirements. The mass CMOS gadget showcase the following parameters, in which the creators follow the scaling methodology like that of the LSTP gadget. The scaling procedure is quickly depicted as follows:

The gadget model has four key scaling parameters: physical entryway length (L-Poly), door oxide thickness (Tox), substrate doping (Nsub), and pinnacle corona doping (Np, halo). These parameters are most significant when deciding key gadget qualities like Vth, on-current, off-current, and entryway capacitance. Notwithstanding these four parameters, Vdd is likewise utilized as an extra handle for altering execution. Every physical measurement other than Tox (source/channel intersection profundity, horizontal source/channel dispersion, radiance measurements, and so forth.) scale with respect to Lpoly. Lpoly is diminished by 30% per age, which concurs well with late Lpoly scaling patterns [6]. A study of ongoing modern distributions shows that Tox has been decreased by ~10% per age underneath the 130 nm innovation hub. In this system, straightforward supposition that Tox decreases by 10% per age has been made. With Lpoly and Tox fixed for every age, the staying three parameters (Nsub, Np, halo, Vdd) might be tuned to coordinate deferral and spillage necessities. The improvement method utilizes delay ( $\tau$ ) as a goal and spillage (I leak, max) as a limitation (it permits spillage to develop by 25% every age, lessens Vdd normally at every age to control dynamic vitality, and upgrades the gadget for least postponement under the spillage imperative).

# EXAMINATION OF VARIOUS DGMOSFET CONFIGURATIONS FOR ULTRA-LOW POWER SUBTHRESHOLD CIRCUIT DESIGN

Presentation of Various DGMOSFET Configurations

DGMOSFETs can either have a three-terminal (3T) arrangement, where both the doors are shorted, or on the other hand a four-terminal (4T) setup, where the back-entryway predisposition is fixed and the front door goes about as a control cathode. On the off chance that the two entryways in the DGMOSFETs are tied (3T), an indistinguishable voltage can be applied to the two doors. Alternately, when the two entryways are autonomous (4T), various voltages can be applied. The asymmetry in the twofold door MOSFET can be realized by various ways. It can be finished by applying distinctive door voltages to front and back entryways, by allocating variety in oxide thickness to front and back entryways. It can likewise be brought by fluctuating entryway material work capacities [7].

Free gate innovation offers an additional terminal in DGMOSFET gadgets at the expense of extra manufacture steps or veils. The additional component of biasing back and front entryways independently offers more adaptability and opportunity to circuit originators utilizing DGMOSFET innovation. The 4T DGMOSFETs show diminished on-current alongside decreased entryway capacitance contrasted with the 3T partners. Besides, 4T DGMOSFETs permit free biasing of the two entryways and offer dynamic edge voltage control (DTC) in circuits. Therefore, autonomous door innovation can be utilized to help trade-off between exchanging capacitance and spillage with circuit delay. Free entryway activity benefits in circuits, for example, Schmitt triggers, dynamic rationale circuits, and sense intensifiers, and static arbitrary access memory (SRAM) bit-cells as showed as of late.

In this work, this will examine four sorts of DGMOSFETs: tied-door symmetric DGMOSFETs (3TSDG), tied-entryway DGMOSFETs (3TADG), free door symmetric DGMOSFETs (4TSDG) and autonomous entryway awry DGMOSFETs (4TADG) Comparison of Various DGMOSFET Configurations HSPICE recreations have been completed utilizing Berkeley Predictive Technology Model (BPTM) for 32 nm DGMOSFET to contemplate the symmetric DGMOSFETs (SDG) and hilter kilter DGMOSFETs (ADG) gadgets and circuit execution with tied-and free door alternatives for

subthreshold activity. The hilter kilter nature of the gadget is being brought by taking the variety in oxide thickness for front furthermore, back entryways. 3T infers that a front entryway (fg) and a back door (bg) are integrated to give the equivalent potential while 4T suggests front and back entryways are applied various possibilities. Gadget parameters separated from the recreations are condensed. 3TDG have better vitality delay item (EDP) execution measurements than 4TDG element, because of the bigger ION/IOFF proportion esteems. Topsy-turvy highlight further improves execution in the 3T choice than in the 4T alternative.

# **ULTRA-LOW POWER RFID RECTIFIERS WITH VARIOUS DGMOSFET CONFIGURATIONS**

As the RFID label is a latent device, DC voltage must be produced to predisposition the circuits of the tag, which is finished by a rectifier. The rectifier changes over a got RF signal into DC voltage. The principle challenge in planning the RFID rectifier is to create the necessary DC power utilizing the low voltage abundancy of the RF signal with worthy force transformation productivity [8].

Different Rectifier Topologies Implemented with DGMOSFETs

### 1. Basic Rectifier:

Force transformation effectiveness (PCE) of a rectifier is characterized by the yield power partitioned by the information power. The PCE of the rectifier circuit is influenced by circuit topology, diodegadget parameters, input RF signal recurrence and sufficiency, and yield stacking conditions. Since the info RF sign of RFIDs in long-go tasks is very little, little turn-on voltage is the most significant factor for the diode gadget. The Scotty diode has been used with a multi-stage design in spite of the extra handling cost due to its little turn-on voltage. The rectifier circuit utilizing the Schottky diode accomplishes a huge PCE, yet it isn't good with the customary CMOS innovation and requires expensive creation handling [9]. Diode-associated n-channel and p-direct MOSFETs are associated in arrangement and the inner hub is associated with RF input terminal through the coupling capacitor (CC). The PCE is nearly dictated by the compelling on-opposition of the diode-associated MOS transistor. The lower the edge voltage of the MOS transistor is, the lower the powerful on-obstruction becomes. In this way the higher PCE is acquired when the edge voltage can be brought down. Be that as it may, the limit voltage can't be brought down altogether since the PCE begins to be constrained by the spillage current.

### CORRELATION OF VARIOUS RFID RECTIFIER TOPOLOGIES USING DGMOSFETS

The previously mentioned rectifier topologies are recreated utilizing HSPICE to investigate the best topology for ultra-low force RFID plan with most noteworthy PCE utilizing DGMOSFET innovation. Examination of DC yield voltages produced by different rectifier topologies actualized with least measured 3T DGMOSFETs with variety in input levels. Traditional and SVC rectifier topologies have practically comparative and lower yield voltages in contrast with higher yield DC voltage produced by the differential drive rectifier. As the RF input signal plentifulness change from 0.1 to 0.9 V (for a force change of  $0.5-365 \mu w$ ),

DC yield power change by 0.5–139 µw for differential drive rectifier and 1.6 pw-1 µw yield power change for a SVC rectifier individually. Therefore, higher PCE values for differential drive rectifier can be found. For a similar change in input voltage level, the PCE changes by 42–38% for differential drive, 0.04–2.1% for SVC and 0.2–2.1% for basic rectifier topologies. Force utilization examination of the above rectifier topologies planned by least estimated 3T DGMOSFETs. SVC and customary rectifier topologies devour lower power (0.01–36 µw for SVC, 0.01–14 µw for ordinary and 0.5–515 μw for differential rectifier topologies RF MOS transistors are normally structured as huge gadgets so as to accomplish the ideal trans-conductance required to meet the RF necessities. They are generally spread out as multi finger gadgets, on the grounds that in profound submicron CMOS forms, the greatest finger length (comparing to the unit transistor width Wf) is restricted. Commonplace gadgets have up to at least 10 fingers. Here the abovementioned least measured gadgets are upsized (multiple times) and recreations are done to see the impact of PCE furthermore, DC yield power created by the different rectifier topologies [10].

It very well may be seen that for a differential drive rectifier, in spite of the fact that the general DC yield voltage produced by upsized gadgets increment essentially (from 0.12–1.72 V), yet the PCE will at present be lower contrasted with least estimated gadgets because of the noteworthy increment in the information power drawn from the sign. In any case, for SVC and basic rectifier topologies, both the DC yield force and PCE increment altogether because of the less number of gadgets and little info power in contrast with that of upsized differential drive rectifier topology. For SVC, DC yield power ascend by 91 PW-5.6µw and PCE by 0.2-4.7% and for regular rectifier, DC yield power increment by 296 PW-4.1 µw and PCE change by 1.2-2.2%. This infers upsizing isn't valuable for differential drive rectifier both as far as PCE and force utilization. For SVC and basic rectifier topologies, the PCE increments in power utilization (0.04-66.4 µw for SVC and 0.03-21.2 µw for regular rectifier). Comparison of DC yield voltages created by differential drive rectifier topology actualized with least and upsized 3T/4T DG MOSFETs with variety in RF input levels is introduced. It tends to be seen that DC yield voltages and in this manner DC power created by 4T DGMOSFET circuits are littler in correlation with that of 3T DGMOSFET circuits for both min. size and upsize topologies. This is basically because of the bigger ION/IOFF estimations of 3T DGMOSFETs than 4T DGMOSFETs, the DC yield power created by the 4T min-size setup is 96% lower at high information levels and 25% lower at little information power levels than the 3T min-sized setup. So also, the 4T upsized arrangement DC yield power level is lower by 114% both at lower and more elevated levels of information power when contrasted with 3T upsized design. Force transformation productivity (PCE) correlations of the differential drive rectifier topology executed with the base and upsized 3T/4T DGMOSFETS with varieties in RF input levels are exhibited. Generally, 4T design has lower PCE than 3T setup, yet at exceptionally little RF input power levels, the expansion in the PCE of the 4T arrangement is seen more than the 3T one.

# CONCLUSION

This paper researched the extent of different arrangements of DGMOSFETs with circuit co-structure for ultra-low force RFID. It exhibited that DGMOSFETs are additionally encouraging for future ultralow force devices in contrast with mass CMOS. Force, postponement, and force delay-item examination of DGMOSFET-based rationale circuits with mass CMOS-based ones show that the DGMOSFET-based circuits improve vitality proficiency over 40% in the subthreshold activity.

The DGMOSFET-based circuits likewise have half less variety than the mass CMOS circuits. From the gadget/circuit execution metrics examinations between four diverse DGMOSFET setups (3TSDG, 3TADG, 4TSDG, and 4TADG), it is seen that the vitality delay-result of the 4T designs is generously higher when contrasted with 3T arrangement. This demonstrates for better generally speaking subthreshold circuit execution, it is desirable over utilize the 3T designs over the 4T setups. The 3TSDG design has around 78% preferable EDP esteem over the 4TSDG setup. The PDP examination of 3T-4T DGMOSFET-based rationale families for subthreshold activity uncovers that sub-CMOS, sub-Domino and sub-DCVSL rationale styles have close by values and lower vitality utilization than the rest rationale families. Sub-CPL and sub-DCVSPG structured with 4TDGMOSFETs are incredibly poor as far as PDP in the subthreshold activity. Generally speaking, the 3TDGMOSFET setup is more qualified to RFID rectifiers and advanced structure squares working in the subthreshold locale than the 4T setup.

## REFERENCES

- J. K. Sahani and S. Singh, 'Design of full adder circuit using double gate MOSFET', in [1] International Conference on Advanced Computing and Communication Technologies, ACCT, 2015.

- V. M. Srivastava, 'Designing of Linear Regulator and Switching Regulator with Double-Gate [2] MOSFET', in 12th IEEE International Conference Electronics, Energy, Environment, Communication, Computer, Control: (E3-C3), INDICON 2015, 2016.

- R. Dastanian, E. Abiri, and M. Ataiyan, 'A 0.5 V, 112 nW CMOS temperature sensor for RFID [3] food monitoring application', in 2016 24th Iranian Conference on Electrical Engineering, ICEE 2016, 2016.

- V. M. Srivastava, K. S. Yadav, and G. Singh, 'Design and performance analysis of double-gate [4] MOSFET over single-gate MOSFET for RF switch', *Microelectronics J.*, 2011.

- [5] S. Singhal, S. Kumar, S. Upadhyay, and R. K. Nagaria, 'Comparative study of Double Gate SOI FinFET and trigate Bulk MOSFET structures', in 2013 Students Conference on Engineering and Systems, SCES 2013, 2013.

- [6] A. Dayal, S. P. Pandey, S. Khandelwal, and S. Akashe, 'Multiple-gate silicon on insulator (SOI) MOSFETs: Device design and analysis', in 2013 Annual International Conference on Emerging Research Areas, AICERA 2013 and 2013 International Conference on Microelectronics, Communications and Renewable Energy, ICMiCR 2013 - Proceedings, 2013.

- [7] B. Iñiguez, R. Ritzenthaler, F. Lime, and B. Nae, 'Simulation and modeling of nanoscale multiple-gate SOI MOSFETs', in Proceedings of the 19th International Conference - Mixed Design of Integrated Circuits and Systems, MIXDES 2012, 2012, pp. 25–29.

- J. Semple, D. G. Georgiadou, G. Wyatt-Moon, G. Gelinck, and T. D. Anthopoulos, 'Flexible [8] diodes for radio frequency (RF) electronics: A materials perspective', Semiconductor Science and Technology. 2017.

- [9] H. Dai, Y. Lu, M. K. Law, S. W. Sin, U. Seng-Pan, and R. P. Martins, 'A review and design of the on-chip rectifiers for RF energy harvesting', in 2015 IEEE International Wireless Symposium, IWS 2015, 2015.

- R. Vaddi, R. P. Agarwal, S. Dasgupta, and T. T. Kim, 'Design and analysis of double-gate [10] MOSFETs for ultra-low power radio frequency identification (RFID): Device and circuit codesign', J. Low Power Electron. Appl., 2011.